# A run-time reconfigurable Network-on-Chip for streaming DSP applications

Nikolay K. Kavaldjiev

#### **Graduation Committee:**

Prof. Dr. P. H. Hartel University of Twente (promotor)

Dr. Ir. G. J. M. Smit University of Twente (assistant-promotor)

Prof. Dr. Ir. Th. Krol, University of Twente Ir. P. G. Jansen University of Twente

Prof. Dr. H. Corporaal Technical University Eindhoven Dr. Ir. K. Goossens NXP Semiconductors, Eindhoven

Prof. Dr. J. Nurmi Tampere University of Technology, Finland

Distributed and Embedded Systems Group P.O. Box 217, 7500 AE Enschede, the Netherlands

This research is conducted within the Gecko project funded by the Dutch organisation of Scientific Research NWO under project number 612.064.103.

This thesis is published in the CTIT Ph.D.-thesis Series No. 06-91 ISSN 1381-3617

This thesis is published in the IPA Dissertation Series under number 2007-02. The current list of titles in the series can be found in the end of this book.

Keywords: network-on-chip, system-on-chip

Copyright © 2006 Nikolay Krasimirov Kavaldjiev, Enschede, the Netherlands

ISBN: 90-365-2410-5

Printed by Wohrmann Print Service, Zutphen, the Netherlands www.wps.nl

# A RUN-TIME RECONFIGURABLE NETWORK-ON-CHIP FOR STREAMING DSP APPLICATIONS

## DISSERTATION

to obtain

the doctor's degree at the University of Twente,

on the authority of the rector magnificus,

prof.dr. W.H.M. Zijm,

on account of the decision of the graduation committee,

to be publicly defended

on Wednesday, 31 January 2007 at 15.00

by

Nikolay Krasimirov Kavaldjiev

born on 3 December 1973

in Sofia, Bulgaria

This dissertation is approved by:

Prof. Dr. P. H. Hartel

(promotor) (assistant-promotor) Dr. Ir. G. J. M. Smit

# **Abstract**

With the advance of semiconductor technology, global on-chip wiring is becoming a limiting factor for the overall performance of large System-on-Chip (SoC) designs. In this thesis we propose a global communication architecture that avoids this limitation by structuring and shortening of the global wires. The communication architecture is used in a multiprocessor SoC for streaming DSP applications. The SoC is intended as a platform for wireless multimedia devices, such as PDAs, mobile phones, mobile medical systems, car infotainment systems, etc.

To improve the performance of the communication in our SoC we use a Network-on-Chip (NoC) architecture. A NoC provides the chip with a high-performance global communication infrastructure, at the same time structures the global on-chip wires and makes their electrical parameters predictable and controllable. By contrast, the bus solutions and the ad-hoc communications solutions used till now in SoC designs result in long wires with unpredictable electrical parameters and require costly design iterations for improving the communication performance.

Our specific NoC uses virtual channel flow control and source routing to provide guaranteed communication services, as well as best effort services. Our NoC is the first on-chip network designed for a run-time reconfigurable system. It offers fast reconfiguration and requires low configuration overhead. Configuring a network path takes less than a millisecond and only costs a few bytes of data overhead. Such time and data overhead is affordable by the run-time reconfigurable SoC for the class of streaming applications we consider.

Our NoC is particularly suitable for the specific traffic conditions created by streaming DSP applications. These applications have a simple structure and create simple traffic patterns but need a high data throughput. The main part of the traffic consists of data streams that require guaranteed services. However, our NoC also supports the small part of the traffic with fine granularity and irregular behaviour that requires only best effort services.

The implementation area of our network router in  $0.13~\mu m$  technology can be as small as  $0.05~mm^2$  depending on the network design parameters. A network channel throughput of several Gbit/s can be achieved, which is enough to satisfy the system applications demands.

The specific contributions of this thesis are:

- 1. We propose a NoC architecture for a run-time reconfigurable multiprocessor SoC that supports streaming DSP applications. To the best of our knowledge, this is the first NoC targeted at a run-time reconfigurable SoC.

- We propose an architecture of a virtual channel router, which in contrast to

conventional architectures is able to provide predictable communication

services and has a lower implementation area cost than conventional

architectures.

3. The predictable performance of our network simplifies the mapping of streaming DSP applications to our multiprocessor system. System reconfiguration can be done in linear time avoiding the NP-complete solutions common for statically scheduled real-time systems. Thanks to this linearity, system reconfiguration can be done at run-time.

# Acknowledgements

At the end of these four years as a PhD student I have to admit that it was not easy. Indeed it was a period in my life when many things have changed, it was the first time for me to live far away from home – an experience that is not always easy to handle. Here I would like to thank to all these people with whom I have worked, from whom I have learned and who have supported me during this long period.

I would like to thank my family and especially my mother Maria and my aunts Rosica and Ilka for their constant support and encouragement. Their love makes me feel near home despite the distance and helps me pass the difficult moments.

First of all, I would like to express my deepest gratitude and respect to my supervisor Gerard Smit. Supporting me in my everyday work, Gerard is always ready to help me, to give me an advice or just talk with me without any reservation, no matter how busy he is. He has been able to sense the slightest signs of doubts and difficulties in my daily work and always was ready to offer his guidance, but in such delicate way that I never lost the feeling of complete freedom in my work.

Although my promoter prof. Pieter Hartel did not work with me on a daily basis I have learned a lot from him. Pieter is highly organised. He always amazes me with his thoroughness and efficiency. Pieter has taught me to be more precise and critical to my work, to question the obvious, and always look for unexpected points of view. He has inexhaustible optimism and enthusiasm. This positive attitude motivates and encourages me to improve.

I am much obliged to Pierre Jansen who has also helped me in my daily work. Pierre has always listened to my problems in patience. He is always willing to discuss and share with me his rich experience. I would like to thank Andre Kokkeler who has reviewed the first draft of the thesis. Andre is a thorough reviewer but with a positive attitude that helped me keeping my motivation. I like to thank Jenna Wells who has also reviewed the thesis and provided me with a lot of helpful suggestions for improvement.

Thanks to our always smiling and cheerful secretaries Marlous Weghorst and Nicole Baveld – always helping and never complaining. No doubt they contribute to the positive working atmosphere.

During these years I have shared the office with a number of different roommates, but the good and friendly atmosphere is always there. Thanks to Gerard Rauwerda, Pascal Wolkotte, Yanqing Guo, Qiwei Zhang for being affable mates and handy source of information. Pascal and I were working on the same subject. Pascal has always been ready to share his view and give me his opinion. Sharing ideas with him helped me to clear my own view.

Thanks also to Bert Molenkamp, Paul Heysters, Omar Mansour, Maarten Wiggers, Marcel van de Burgwal, Philip Hölzenspies and the other group members for the nice working atmosphere and for the chats. It was always nice to chat about the everyday life with Lodewijk Smit and Michel Rosien. It was kind of a pressure release and a way to know the Dutch habits better.

This thesis is based on the ideas developed in the Chameleon project and would not be possible without the contributions of the members of this project. The ideas presented here are directly related to the results obtained by Paul Heysters, Lodewijk Smit, Gerard Rauwerda and Pascal Wolkotte.

Working at University of Twente gave me the opportunity to meet many interesting people all over the world: Ricardo Corin and Laura Brandán Briones, Vasughi Sundramoorthy, Cheun Ngen Chong (aka Jordan), Supriyo Chatterjea, Gabriele Lenzini, Damiano, Kavitha, Ozlem, Anka, Marchin, Tim, Stefan, Ileana, Raluca, Mihai, Roland, Mohammed, Sinan, etc., etc...

Vasughi and Ricardo were the first people I knew in Enschede. They have introduced me to the Dutch culture and gave me some important tips and tricks for survival. I remember my first day in Enschede, Vasughi took advantage on my innocence and prepared a welcome dinner for me – a typical Malaysian meal. During the dinner, proudly looking at me and Ricardo crying over the extremely spicy dish, she started giving us advice how to extinguish the "'fire" in our throats: "It is useless with beer or water, it does not work; better try sweet juice, it is most effective ...". As far as I know there are many people who have the same experience with Vasu's spicy meal.

Jordan has been my sport mate for a long time and this gave me the opportunity to know him better. To him I owe my introduction to the Chinese culture and kitchen. Jordan is a friend that cares and often has given me his moral support.

For a short time after his arrival, Supriyo and I were living in the same house. Supriyo has shared with me that his impression then about Bulgarians was formed only by watching strugglers and heavy weight lifters on sport TV programs. I was the first real-life Bulgarian he met and more importantly he had to live with and understandably this thought caused him some worries. In my opinion everything went well and I have nice memories from that period. Supriyo was the first Singaporean I met too. He is a very intelligent person addicted to fish.

An important part of my life in Enschede is the Bulgarian community there: Vania, Stanislav, Chris and Aleks, Zlatko Zlatev, Christian Tzolov, Ivan Kurtev, Nikolay Diakov, Julia Bachvarova, Natasha Jovanovich, Georg Koprinkov, Samuil Angelov, Boris Shishkov, Boriana Rukanova, Danail Rosnev, Robina, Snoopy. It is true than not all of them are Bulgarian but all of them helped me feel like at home and manage with the unavoidable homesickness and the consequence of the sunshine shortage. Here I would like to thank to two special friends of mine without whom my life in Enschede would have been completely different - Vania and Stanislav Pokraevi. This family has supported me in the difficult moments of my stay in Enschede. Their inexhaustible positive attitude has assured me that there is nothing to worry about. They kept reminding me about the nice things in life that are worth dreaming of, e.g. boza and milinki. They have inspired and encouraged my cooking attempts and other undertakings in my life. Recently Vania and Stanislav have been introduced to a completely new experience – being parents of the twins Alex and Chris (aka The Boys). As a witness of the progress of the parents and the boys since the very beginning, I can firmly say that Alex and Chris are the most beloved boys I have ever seen. Doubtless, these are boys with a bright future, children that will bring a lot of happiness in their parents' life.

Finally I want to thank my best friends Kristian, Tania and Kristin, Sasho and Stefka, Strahil, Rostislav and Krasi, Rusi, Nadia, Milena, Koko, etc. for being with me all this time despite the long distance between us. They are among the things that make my country and my city of birth the best place to be, the place I will always want to return to. I also have to thank Skype and Internet in general for make the earth smaller and bringing the people I love close to me.

# Contents

| Abstract   |                                             | i  |

|------------|---------------------------------------------|----|

| Contents   |                                             | v  |

| Chapter 1  | Introduction                                | 1  |

|            | luction                                     |    |

| 1.2. Netwo | ork-on-Chip concept                         | 1  |

| 1.3. Appli | cation domain                               | 2  |

|            | treaming DSP applications                   |    |

| 1.3.2. H   | leterogeneous tiled SoC architecture        | 4  |

|            | ynamic reconfiguration                      |    |

|            | Centralised control                         |    |

|            | conductor technology trends                 |    |

|            | ignal integrity problem                     |    |

|            | Clock distribution problem                  |    |

|            | roductivity gap                             |    |

|            | Directions                                  |    |

|            | tives                                       |    |

|            | ibutions                                    |    |

|            | ture of the thesis and related publications |    |

| Chapter 2  | Background and related work                 |    |

|            | luction                                     |    |

|            | characteristics                             |    |

|            | onnection networks                          |    |

|            | Direct and indirect networks                |    |

|            | erformance of interconnection networks      |    |

|            | letwork topologies                          |    |

|            | low control                                 |    |

|            | outing                                      |    |

|            | Quality of Service (QoS)                    |    |

|            | ork-on-Chip solutions                       |    |

|            | Circuit switching solutions                 |    |

|            | acket switching solutions                   |    |

|            | Clockless solutions                         |    |

|            | ummaryusion                                 |    |

|            |                                             |    |

| Chapter 3  | Network-on-Chip architecture                |    |

|            | luction                                     |    |

|            | hhole router architecture                   |    |

|            | al channel router                           |    |

|            | arce allocation in a VC router              |    |

| 3.4.1. V   | C allocation                                | 50 |

| 3.4.2. S                                             | witch allocation                                       | 52        |

|------------------------------------------------------|--------------------------------------------------------|-----------|

| 3.5. Providing service guarantees at a network level |                                                        |           |

| 3.6. System level support                            |                                                        |           |

|                                                      | ations                                                 |           |

|                                                      | etup                                                   |           |

|                                                      | esults                                                 |           |

|                                                      | parison                                                |           |

|                                                      | lusion                                                 |           |

|                                                      |                                                        |           |

| Chapter 4                                            | Implementation                                         |           |

|                                                      | luction                                                |           |

|                                                      | mentation details                                      |           |

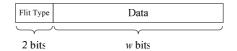

| 4.2.1. F                                             | lit and packet format                                  | 64        |

|                                                      | Channel interface                                      |           |

| 4.2.3. In                                            | nput controller                                        | 66        |

| 4.2.4. V                                             | 'C allocator                                           | 68        |

| 4.2.5. S                                             | witch allocator                                        | 70        |

| 4.2.6. R                                             | ound-robin arbiter                                     | <i>75</i> |

| 4.3. Synth                                           | esis results                                           | 76        |

| -                                                    | lusion                                                 |           |

| Chapter 5                                            | Evaluation of the virtual channel reservation approach | 83        |

| 5.1. Introd                                          | luction                                                | 83        |

| 5.2. Netwo                                           | ork and GS services                                    | 84        |

| 5.3. Routi                                           | ng function                                            | 87        |

|                                                      | peration                                               |           |

|                                                      | lgorithms                                              |           |

|                                                      | Overhead                                               |           |

| 5.4. Spatia                                          | al model of the GS traffic                             | 92        |

|                                                      | ation experiments                                      |           |

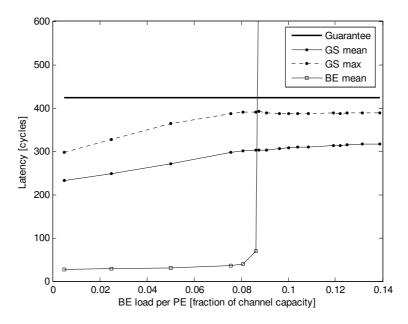

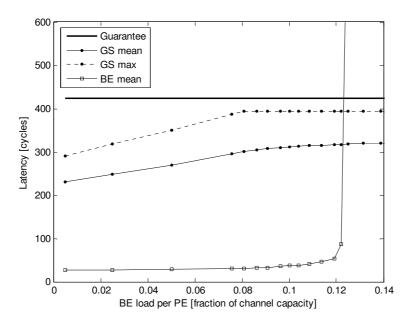

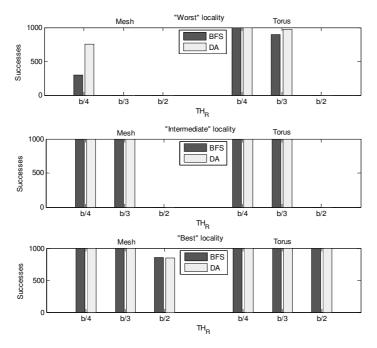

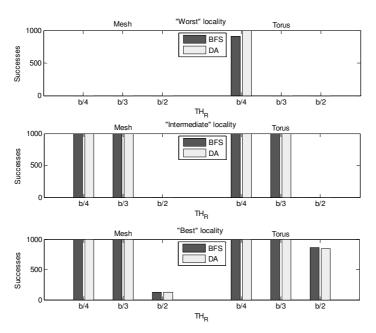

|                                                      | ation results                                          |           |

|                                                      | Jumber of successful samples                           |           |

|                                                      | Detour cost                                            |           |

|                                                      | Communication energy cost 1                            |           |

|                                                      | Performance in the presence of BE traffic              |           |

|                                                      | lusion1                                                |           |

| Chapter 6                                            | Network integration 1                                  |           |

| 6.1. Introd                                          | luction                                                | 109       |

|                                                      | m operation1                                           |           |

|                                                      | tarting an application                                 |           |

|                                                      | cheduling approaches                                   |           |

|                                                      | imed operation                                         |           |

|                                                      | F graphs and MCM analysis                              |           |

|                                                      | eting throughput of an application                     |           |

|                                                      |                                                        |           |

|                                                      | Throughput of a single application task                |           |

|                                                      | Comparison                                             |           |

| 6.6. Throu                                           | ghput of the whole application                         |           |

| n / Hyam                                             | nie.                                                   | 123       |

| 6.8. Conclu  | sion       | 124 |

|--------------|------------|-----|

| Chapter 7    | Conclusion | 127 |

| Bibliography |            | 131 |

# Chapter 1

# Introduction

# 1.1. Introduction

In 1965, Intel co-founder Gordon Moore made a prediction, popularly known as "Moore's Law", which states that the transistor density on integrated circuits (IC) doubles about every two years [57]. For four decades silicon technology has been following this law and the number of transistors on a chip has been increasing exponentially. Today, it is commonly believed that from a purely technological perspective there are no obstacles to invalidate Moore's Law in the next decade [93].

The higher integration level achieved following Moore's law allows more and more functionality to be accommodated on a chip. It is now possible to integrate a complete electronic system, including its peripherals and all interfaces, on a single die. Such a system is known as a System-on-Chip (SoC).

Although there are no obstacles for the semiconductor manufacturing technology to continue reducing the IC feature size and increasing the IC integration level, there are several emerging IC design problems that prevent the full utilization of the technology potential. These problems are caused mainly by the smaller feature size and the high integration level. To continue exploiting the technology efficiently they must be overcome. This thesis addresses the main two of these emerging design problems:

- the lower performance of the global on-chip wires, which make the global communications in large SoC designs a performance limiting factor.

- the high design complexity resulting from the higher integration density, which makes SoC design an inefficient and time-consuming task.

We address these problems in the context of a specific class of large SoC architectures – a multiprocessor SoC for streaming Digital Signal Processing (DSP) applications. The solution we propose for such systems is a Network-on-Chip (NoC) communication architecture. A NoC replaces the slow ad-hoc global on-chip wiring with a high performance communication infrastructure which facilitates structured modular system design and thus helps reducing the system design complexity.

# 1.2. Network-on-Chip concept

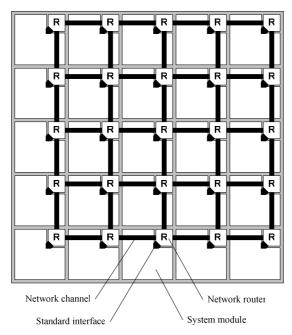

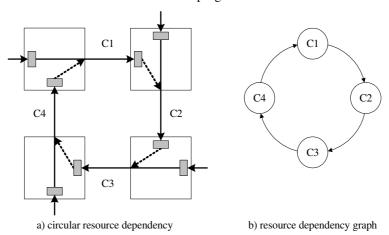

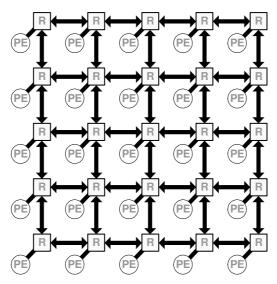

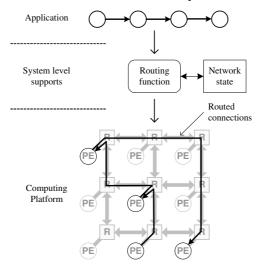

A NoC [17, 25, 45, 60] is a lightweight communication network that interconnects the system modules replacing the traditional on-chip bus. An example SoC employing a NoC is shown in Figure 1.1. The chip area is divided into square *tiles*. Each tile contains a system module (e.g., a processor, DSP, peripheral controller, memory subsystem, etc.). Such a system is referred to as a *tiled system* [25]. The NoC is built of *routers*

interconnected by network *channels*. Each tile is connected to a network router through a *standard interface*. Tiles communicate only by sending messages over the network through their interfaces.

Figure 1.1: An example SoC architecture employing an on-chip network

The NoC serves as a global communication infrastructure. It provides shared global interconnects that can be highly optimised since its development cost can be amortised across many designs. The NoC can provide short and structured global wires with well controlled electrical parameters. This eliminates time consuming design iterations for improving the signalling performance and enables the use of high performance circuits to reduce the communication latency and increase the bandwidth [41, 88]. The network supports parallel communication, so a high aggregate bandwidth can be obtained. Increasing the number of modules in the system also adds routers and channels; hence, the aggregate bandwidth scales with the size of the system. By offering a standard interface, the network facilitates the reusability and interoperability of modules.

# 1.3. Application domain

The NoC proposed in this thesis is used in the Chameleon project [39]. The Chameleon project aims to design a dynamically reconfigurable multiprocessor SoC for wireless multimedia systems. Potential application areas for such a platform are mobile multimedia devices (e.g., PDAs, mobile phones), mobile medical systems, on-board multimedia systems, smart sensors (e.g., remote surveillance cameras), etc. These systems have to meet challenging requirements such as: high performance, low power consumption, support for Quality-of-Service (QoS) and small size. As part of the system, the NoC must also contribute to these requirements.

Below we summarise the architecture of the SoC defined by the Chameleon project. We focus on the aspects relevant to the NoC design. We start with typical system applications and then present the system architecture. Later we briefly discuss the organization and the operation of the system.

# 1.3.1. Streaming DSP applications

The majority of applications in our application domain are streaming DSP applications. Examples of such applications are wireless baseband processing applications (e.g., HiperLAN/2, WiMax, DAB, DRM, DVB) and audio/video processing applications (e.g., MPEG codecs). Streaming DSP applications operate on streams of continuously arriving data items which are processed one by one in the order of their arrival and the results are released as an output stream.

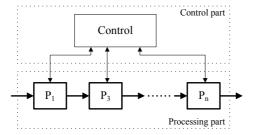

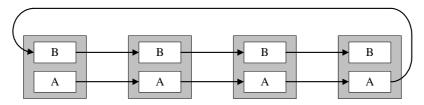

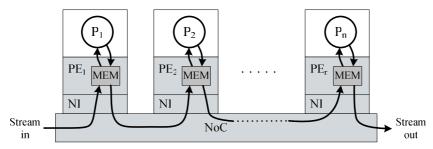

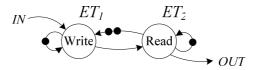

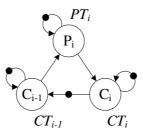

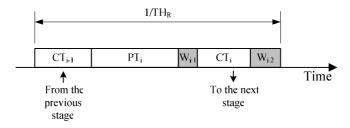

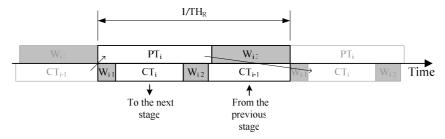

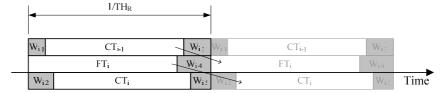

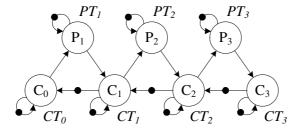

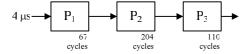

Typically, streaming DSP applications are structured as shown in Figure 1.2 [23, 67, 87]. Two parts can be recognized in this structure – a *processing* part and a *control* part. The processing part consists of a number of processing blocks,  $P_i$ , arranged in a pipeline. The streamed data items pass through the pipeline and each processing block there applies some transformation on them. Typically, the transformations are mathematical algorithms, such as Fast Fourier Transforms (FFTs) or Discrete Cosine Transforms (DCTs), demanding intensive computation. Therefore, the processing part has high computational demands. Since data items pass through the pipeline periodically, the processing blocks show repetitive timing behaviour. Because many applications process streams in real-time, their processing part requires performance guarantees and the pipeline throughput has to be guaranteed. Hence, the processing part demands Quality-of-Service (QoS) guarantees.

Figure 1.2: Typical structure of a streaming DSP application

The control part of the application implements the control functions associated with adaptation and efficient operation. For example, in a wireless baseband processing application, the control part could monitor the error rate of a communication channel and change the modulation scheme to increase the throughput or to reduce the required computation power. The control part shows more reactive and irregular behaviour and requires little computation. As long as the control part only improves the application efficiency by adding adaptability, its performance is not critical to the real-time operation of the entire application [71]. Hence, the computation and communication in the control part do not require strict performance guarantees.

Streaming DSP applications are computationally intensive, but they have a relatively simple structure. The aim of the Chameleon project is to provide a multiprocessor platform that exploits this simple parallelism naturally present in the pipeline structure of these applications. The potential of the simple pipeline structure to

simplify the design of predictable multiprocessor systems has also been recognized by others [49, 69]. The simple application structure simplifies a number of organisation issues in the Chameleon multiprocessor system. Because parallelism is naturally present in the application structure, partitioning the application into parallel tasks is straightforward. The simple data dependencies between the tasks ease the scheduling of applications on multiple processors. The running applications also generate simple communication patterns, which, as we shall see, help to achieve predictable communication behaviour. In general, the regular parallelism in streaming applications facilitates achieving a predictable and guaranteed operation of multiprocessor systems. Since the majority of applications running on our multiprocessor system are streaming DSP applications, this is the type of parallelism we consider.

Running a streaming DSP application on multiple processors entails mostly streaming communication between the processors. The communication will last for the duration of the application, which for our application domain is estimated from seconds to hours, e.g., watching a film, making a phone call, using a wireless communication channel, etc. Therefore, the traffic in the system consists of semi-static data streams.

The throughput of the data stream between the tasks in the processing part is application dependent. For more demanding applications the throughput is hundreds of Mbit/s. For example, a HiperLAN/2 receiver processes a stream demanding 512 Mbit/s [67]. The size of the data items is also application dependent, for example, it can be a 14-bit audio sample from an analogue-to-digital converter (ADC) or 1024×1024×24-bit video frame. Since often streams are processed in real-time, this traffic requires performance guarantees.

In contrast to the stream processing part, the communication in the application control part consists mainly of short control messages – several bytes of control or state information. To estimate the control traffic, we make the following assumption – each task in the processing part of a HiperLAN/2 receiver generates and receives a 10 Byte control message for every processed data item. This is an overestimation since most tasks do not communicate control messages for every data item. The control traffic generated by the application is then estimated at 10% of the total traffic, while the remaining 90% is streaming traffic. This is a rough estimation that gives the maximal amount of control traffic in the system. The estimation for other baseband processing applications and also for video applications gives similar results.

Thus, we assume the following model for the system traffic generated by streaming DSP applications: 90% of the traffic consists of high throughput semi-static streams that require communication guarantees; 10% of the traffic consists of fine granular control messages that require no strict service guarantees.

## 1.3.2. Heterogeneous tiled SoC architecture

The SoC proposed in the Chameleon project has a tiled architecture (Figure 1.1). The tiles are heterogeneous reconfigurable processing elements (PE). A tiled architecture has a number of advantages. It can achieve high performance because it supports massive parallelism. It is a future-proof architecture because the tiles do not grow in complexity with technology; instead, the number of tiles on the chip grows. The energy efficiency is improved by switching off tiles that are not used. Defective tiles can be switched off and isolated, which makes the architecture fault-tolerant.

In a heterogeneous system algorithms run on the type of PE which performs the required computation most efficiently. For example, some algorithms run more

efficiently on bit-level reconfigurable PEs (e.g. pseudo random generators), some on word-level reconfigurable PEs (e.g. FIR filter, FFT). Hence, the type of the PEs building the system is chosen according to the needs of the application domain.

Most of the tiles in our system are domain specific PEs, designed to perform fast and efficiently the DSP algorithms in the processing part of streaming applications. Because the DSP algorithms are mostly compute intensive and run periodically, multitasking is inappropriate. Hence, the domain specific PEs are single task processors. One or a few tiles in the system are multi-tasking general purpose processors (GPP), to run the control part of the applications and also system control tasks.

Each PE has its own local code and data memory. This reduces the need to access the shared global memories that can easily become a bottleneck in a streaming multiprocessor architecture. Since the communications between the PE and the shared global memory are reduced, the traffic and communication energy are reduced as well.

The number of tiles that will fit on a chip is estimated by comparing the maximal chip size with the tile size. Assuming the maximal chip size for the current and the next generation technologies is  $26 \times 22 = 572$  mm<sup>2</sup> [93]. For a tile size estimation we use the area of the Montium tile processor [39, 40] – a domain specific processor for baseband processing applications. The area of the Montium tile processor together with its local memories (data and code) in  $0.13\mu m$  technology is  $2 \text{ mm}^2$ . Hence, more than 200 such tiles will fit on a single chip. This number will increase exponentially with the coming generations of semiconductor technologies. Therefore, it is not unrealistic to consider arrays of hundreds of tiles [14].

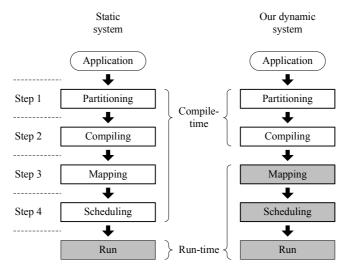

## 1.3.3. Dynamic reconfiguration

In a tiled architecture, each tile is reconfigured independently; the tile is the natural unit of partial reconfiguration. Unlike other state of the art systems, in our system the reconfiguration is done at run-time. While some tiles are performing tasks, unused tiles can be configured for new tasks. Therefore the system is dynamically reconfigurable.

Dynamic reconfiguration is essential to support the dynamically changing demands of the application domain: the system operates in a constantly changing environment. The user demands change (e.g., starting/terminating applications), the environmental conditions change (e.g., available networks, wireless channel conditions) and the available power budget also changes (decreasing battery budget or connected to the mains). The set of running applications and tasks in the system adapts dynamically to these changes.

The run-time reconfiguration modifies the system communication demands. For example, a new data stream may be needed or some of the old streams may be redirected or replaced. The NoC must be able to handle such dynamically changing traffic conditions. Run-time changes in part of the traffic must be possible without disturbing the rest of the traffic. The network reconfiguration time must be short enough to enable adequate system reaction time and reconfiguration must be transparent to the user.

#### 1.3.4. Centralised control

Tiles are configured by configuration messages. Generally, configuration messages may come from any tile or from outside the system. However, during normal system operation, configuration messages are generated only by the one tile responsible for

system run-time configuration, control and management. This tile acts as a central authority that manages the other tiles by configuring them. Therefore our system operates with centralised control. Because the central tile performs mainly control oriented tasks, it is appropriate for this tile to be a GPP.

The centralised control has the following advantages for our system. As a consequence of the centralized control, most of the tiles can be simple since they are not required to perform distributed control functions; all control functions are performed by the central tile. The central tile has a global view of the system and can distribute the system resources more efficiently. The central view facilitates also the QoS support and the system performance optimisation.

Drawbacks attributed to centralised control are its poor scalability and unreliability. However, these disadvantages can be avoided to some extent by adding more GPP tiles to the system. As the system size grows, the central GPP tile can delegate some tasks to subordinate GPPs and avoid scalability problems. In case of a malfunctioning central GPP, its functions can be taken over by another GPP with similar capabilities. However, making the centralized control in our system reliable is beyond the scope of this thesis.

The central tile starts and stops applications at run-time. To start an application, the central authority allocates and configures tiles for the application tasks. The procedure of tile allocation is referred to as *application mapping*. For the purpose of mapping, the applications are partitioned into tasks with appropriate granularity to run on tiles; this happens at compile time. At run-time, the mapping algorithm chooses the exact tiles where the task will run. By mapping communicating tasks on neighbouring tiles, the communication distances are reduced (or the communication locality is improved). As a result, the traffic and the communication energy are reduced.

A mapped application task communicates only with some of the other tasks of the same application and eventually with the central authority. Thus, it is not expected that a tile addresses other tiles randomly. Therefore, during its operation a tile needs to know only a small, fixed set of addresses of the other tiles.

The configuration messages also contribute to the system traffic. However, they form a small part of it. The configuration message size depends on the configuration space of the tile being configured. For domain specific tiles this space is usually several KBytes. For example, the total configuration space of the Montium tile is 2.6 KByte [39]. Tile configuration is required when an application is started. For applications such as wireless channels, video/audio players, etc., this may happen every several seconds or several hours. To estimate the amount of configuration traffic in the system, we use the HiperLAN/2 receiver again [67]. Assume that a new receiver is instantiated as an application every second (this is a strong overestimation, since it is not realistic that a new wireless channel is required every second). A HiperLAN/2 receiver is mapped on three Montium tiles [67]. To configure the new tiles, configuration messages of size at most 2.6 KByte are generated every second and these messages generate traffic of 20.8 Kbit/s per tile. Compared to the per-tile throughput of the main data stream which is 512 Mbit/s, the configuration traffic is estimated to be less than 0.005% of the total traffic. Thus, even with a strong overestimation, the fraction of configuration traffic in the system is negligibly small. Whether configuration messages require communication guarantees depends on whether the start-up time or adaptation time of an application is critical.

# 1.4. Semiconductor technology trends

The design of a large SoC like the one we consider in this thesis faces problems related to the global on-chip wiring. These problems are a result of the reduced dimensions in the new generation of semiconductor technology. The reduced dimensions change the electrical parameters of wires and cause two problems referred to as the *signal integrity problem* and the *clock distribution problem*. Another problem, referred to as the *productivity gap*, relates to the need for a more productive design methodology in order to cope with the increasing design complexity. We discuss each of these problems in the subsequent sections.

# 1.4.1. Signal integrity problem

The basic components of a digital CMOS IC are gates and wires. The gates do signal switching while the wires transport signals. Every silicon technology generation reduces the dimensions of gates and wires and so changes the physical and thus their the electrical properties. While in the previous technology generations these changes did not lead to serious complications, now they are recognised as a problem that requires urgent attention [42, 55, 76].

As the base fabrication technology shrinks to smaller dimensions, the gates become smaller and the wires become thinner and, as a result, the signal delay of gates and wires changes. Under scaling, the delay through a fixed-length wire (which is inversely proportional to the signal propagation velocity) increases, while the gate delay decreases. Thus, an increasing disparity between wire and gate delay is observed, assuming constant wire length.

Typically, IC designs consist of a number of modules. As designs scale to the newer technologies, modules get smaller, the wires in the modules get shorter and the relative change in the delay of wires to the delay of gates in a module is modest. However, a chip can accommodate more and more modules, which are also interconnected by wires. These wires communicate signals across the entire chip and in contrast with the local module wires their length does not scale with technology. They stay long and their delay scales upwards relative to the gate delay. Thus, we must distinguish two types of wires, the signal delay of which is influenced differently by the scaling. We refer to these two types as *local* and *global* wires.

If no special measures are taken, it might be expected that future ICs will consist of fast high-performance modules, interconnected by slow global wires. Thus the global wires will become a system bottleneck and will degrade the overall IC performance. Researchers agree that a solution to the problem can be provided by a new chip design methodology [42]. In the current methodology the chip wiring is automatically generated by the design tools and the designers cannot control the wires in the early design stages. The automatically generated wires are not structured and their electrical parameters, such as parasitic capacitance and crosstalk to adjacent wires, are difficult to predict early in the design process. This does not allow for optimisation of the global wires in early design stages and leads to many time consuming iterations in the late design stages.

Instead of assuming the wiring as something hidden and automatically generated by tools, researchers agree that *explicit structures that handle the inter-module communications* must be included in the system architecture. Such an approach will make global wires structured and controllable; it will make the global communication

latencies explicit and predictable in an earlier design stage and will allow particular measures to be taken for their improvement.

# 1.4.2. Clock distribution problem

The changes in the electrical properties of wires also affect the on-chip global clock distribution. It is getting more and more expensive in terms of energy to distribute a precise clock signal to all modules on the chip. For example, in complex high performance chips, clock distribution may cost near 50% of the total energy consumption [79]. Hence, chip-wide synchronous operation is becoming expensive. The envisioned solution is the *Globally Asynchronous Locally Synchronous* (GALS) systems design framework [19, 58]. A GALS system is a system consisting of many synchronous modules, which, however, operate at their own local clock frequencies. No global clock distribution is required and the system should be considered globally asynchronous. The synchronous modules are often referred to as *clock islands*.

Compared to a fully synchronous design, GALS can reduce the clock distribution power by 70% [38]. Another advantage of GALS is that the system modules are still synchronous and can be designed using standard tools and methodology. To complete the framework, asynchronous communication techniques for transporting data between the islands are required.

# 1.4.3. Productivity gap

As the integration level increases, the chip complexity grows. However, the chip complexity growth rate is about two times higher than the design productivity growth rate [46]. This means that the system design time will increase exponentially if the current design methodology and tools are not replaced by more productive ones. A complex design now can easily include 20-million logic gates. If such a design is started from scratch, it could easily take 200 engineers three to five years to architect, design, verify and build [82]. At the same time a common wisdom is that the product design cycle needs to be approximately one year to be competitive in the market.

The disparity between the complexity and the productivity growth rates is usually referred to as productivity gap. To narrow this gap, more productive methodologies are needed. We can already observe that driven by this need the design methodology changes. Instead of designing systems from scratch, currently more and more systems are built from existing modules (re-use), e.g. CPUs from ARM and MIPS, common I/O blocks such as Ethernet MAC, USB, PCI, etc. It is expected that future systems will consist mainly of pre-designed standard IP (Intellectual Property) modules, adding only a few proprietary modules. Hence, future system design will consist mainly of integration of pre-existing IP modules. These systems will need an integration technology that facilitates modularity and IP interoperability. Adding, removing or changing an IP module should be possible without major disturbances of the rest of the design. This can be achieved by using standard global on-chip communication architecture offering a standard interface to the IPs. By reusing the communication architecture over many designs, design time and cost are saved. Since the communication architecture is optimised and with a fixed layout, time consuming iterations for optimising the global communications are avoided when a new SoC is designed or when an old is modified by replacing or adding modules.

## 1.4.4. Directions

For continued benefit of the advances in silicon technology, all three design problems addressed above must be solved. We believe that the three problems can be solved in principle by an explicitly defined global communication infrastructure that structures and shortens the global wires and facilitates modular design.

Current complex on-chip systems are also modular, but most often the modules are interconnected by an on-chip bus. The bus is a communication solution inherited from the design of large board- or rack-systems in the 1990's. It has been adapted to the SoC specifics and currently several widely adopted on-chip bus specifications are available [89-91, 95].

While the bus facilitates modularity by defining a standard interface, it has major disadvantages. Firstly, a bus does not structure the global wires and does not keep them short. Bus wires may span the entire chip area and to meet constraints like area and speed the bus layout has to be customised [78]. Long wires also make buses inefficient from an energy point of view [9]. Secondly, a bus offers poor scalability. Increasing the number of modules on-chip only increases the communication demands, but the bus bandwidth stays the same. Therefore, as the systems grow in size with the technology, the bus will become a system bottleneck because of its limited bandwidth.

The current solution for the bus performance and scalability problems is bus partitioning. A bus is partitioned into several busses (most often two), connected trough bridges. A hierarchy may be introduced between the busses, e.g. a high-performance system bus and a low-performance peripheral bus. While the partitioned bus solution is satisfactory for the current system sizes (up to tenths of IPs) it does not help for structuring the chip layout.

Although the bus is the common communication solution in the current SoC, its future application is questionable because a bus is unable to solve the design problems foreseen for the future semiconductor technology. Therefore a communication paradigm shift is required. A new SoC communication solution that addresses the design problems is needed.

We believe that an appropriate solution can be found in the communication concept used in the 90's for the interconnection of processor arrays in multi-computers. In multi-computers many processors are interconnected by a communication network. It is proposed to use such a network to interconnect the modules in a SoC [25]. This concept has become popular as a Network-on-Chip (NoC). The cost of applying an interconnection network on-chip is the area overhead due to new system components (routers) needed to support the network. The system organisation must also take into account the network and may incur additional network exploitation costs in terms of configuration and time overhead.

# 1.5. Objectives

The arguments presented suggest that NoC structures have the potential to solve the key design problems in the future semiconductor technologies and motivate us to use a NoC as an on-chip communication infrastructure in our SoC design. However, there are still many open questions which have to be answered in order to show that the NoC concept is feasible. For example, to design a NoC, one has to decide which particular network techniques to employ. It is not known what performance can be achieved by a NoC and whether it can satisfy the system demands. It is not known whether the costs

of employing the NoC are acceptable. It is still not clear whether the network can support the overall system operation requirements.

These are the questions we address in this thesis. Our objective is to define an NoC architecture, evaluate its performance and estimate its implementation cost. Therefore we define the following research questions:

1. What network techniques are appropriate to minimize the network overhead while maintaining satisfactory performance?

This question addresses the design choices that have to be made. The design objective is to achieve a network performance that satisfies the system demands. We consider the typical network performance metrics throughput and latency, but also the services the NoC can provide e.g., guaranteed services or best effort services. The design constraint is given by the maximum acceptable network overhead. We consider two types of overhead – *implementation* and *exploitation* overhead. The implementation overhead comprises all the costs due to the physical implementation of the network; these are the area cost and the static energy cost. The exploitation overhead comprises all the costs for network support and exploitation, e.g. network configuration costs, costs for sending data over the network (dynamic energy cost and data overhead), etc.

The design choices are made on the basis of comparison between the relative cost and performance of the considered techniques and not the actual implementation performance and cost. For example, latencies are compared in terms of clock cycles but it is not taken into account what the maximal achievable operating frequencies are. Therefore, to evaluate the network we have to find its actual cost and performance and that leads to our second question:

#### 2. What is the overhead and the performance of a NoC architecture?

This question addresses the evaluation of the implemented network and its answer requires estimation of all the costs the NoC employment entails. To estimate the exploitation overhead it is necessary to know exactly how the network is used by the system. Hence our third question is:

# 3. What is the optimal use of the NoC?

This question addresses the overall system operation and all the interactions between the NoC and the system. It is a difficult question to be answered in detail since it involves many aspects of the system operation which are beyond the scope of the thesis. However, we propose a system organization scenario that supports the NoC communication concept as much as possible.

In general, this thesis presents a proof of concept of the NoC idea. We define and evaluate an instance of a NoC architecture for our tiled Chameleon SoC. The NoC is not a general purpose one but aimed to support the streaming DSP applications in our system.

# 1.6. Contributions

The scope of our work is given by the Chameleon system [39, 71]. In this scope we provide a feasible NoC solution. The specific contributions of this thesis are:

- 1. We propose a NoC architecture for a run-time reconfigurable multiprocessor SoC that supports streaming DSP applications. To the best of our knowledge, this is the first NoC targeted at a run-time reconfigurable SoC.

- We propose an architecture of a virtual channel router, which in contrast to

conventional architectures is able to provide predictable communication

services and has a lower implementation area cost than conventional

architectures.

- 3. The predictable performance of our network simplifies the mapping of streaming DSP applications to our multiprocessor system. System reconfiguration can be done in linear time avoiding the NP-complete solutions common for statically scheduled real-time systems. Thanks to this linearity, system reconfiguration can be done at run-time.

# 1.7. Structure of the thesis and related publications

The rest of the thesis is organized as follows. In Chapter 2, we review communication network techniques and select those suitable for our NoC implementation. We choose to use a virtual channel network. In this chapter we also discuss some recent work on NoC design.

In Chapter 3, we discuss the possible architectural solutions for a virtual channel router. We study the influence of the architecture on the router performance and identify those architectures that can provide predictable communication services. Finally, we propose an approach for providing guaranteed communication services at network level. Major parts of this chapter have been presented at the IEEE International Symposium on VLSI 2006 [6].

Implementation details about the selected router architecture are presented in Chapter 4, in which we propose an implementation that simplifies the design and reduces the overall router area. Implementation results are also presented there. Major parts of this chapter have been presented at the IEEE International System-on-Chip Conference 2004 [5] and at the EUROMICRO Symposium on Digital System Design 2004 [1]

In Chapter 5, the proposed approach for providing guaranteed services is evaluated with a model of the expected traffic in the system. Also the overhead for applying the approach is estimated. Major parts of this chapter have been presented at the International Workshop on Applied and Reconfigurable Computing 2006 [7].

Chapter 6 shows how performance guarantees are given to streaming DSP applications. Major parts of this chapter have been presented at the EUROMICRO conference on Digital System Design 2005 [4] and at the Communicating Process Architectures Conference 2005 [8].

Chapter 7 gives conclusions and recommendations.

# Chapter 2

# Background and related work\*

Multiprocessor networks have been studied for more than two decades and a solid foundation of design techniques is available. In this chapter we review the main techniques for interconnection networks. We also present some recent network-on-chip solutions and discuss the techniques they employ.

# 2.1. Introduction

The objective of this thesis is to define a Network-on-Chip (NoC) architecture for the tiled multiprocessor System-on-Chip (SoC), described in Chapter 1. The task of the NoC is to interconnect a set of processing tiles, allowing them to exchange data and to operate as an integral system. Building networks of processors is not a new research topic. Such networks have been investigated for more than two decades in the domain of parallel computing and are known as Multiprocessor networks (MP networks). As a result, a solid foundation of design techniques for MP networks is available in the literature. Since by nature on-chip networks are MP networks, MP network techniques can be adopted for building NoC architectures. However, on-chip networks have their specifics, which are result of the different realization technology and the different requirements of the multiprocessor system and the applications running on the system. These specifics must be taken into account when adopting MP network techniques.

This chapter consists of three parts. In the first part we discuss the NoC specifics in comparison with MP networks. In the second part we give an overview of the general interconnection network techniques, focusing on the techniques used for building MP networks. We discuss the techniques in the context of our tiled multiprocessor system. Our objective is to identify those of them which are most suitable for use, directly or after modification, in our NoC and also to identify potential gaps which require development of new specific techniques. We also introduce terminology and notation used in the other chapters. We adopt the terminology and notation used by Dally and Towles [27].

The third part of this chapter is devoted to existing NoC solutions. We discuss only the most mature solutions and techniques that are relevant to this thesis. The solutions are compared mostly qualitatively; the quantitative comparisons are restricted to chip area and clock frequency (when this information is available). We restrict our quantitative comparisons, because often NoC solutions are targeted at different systems, address different traffic types and pursue different goals, or detailed information about

<sup>\*</sup> Major parts of this chapter have been presented at the PROGRESS Embedded Systems Symposium [2].

the system is not available. Therefore, detailed quantitative comparison cannot be made fairly.

# 2.2. NoC characteristics

To establish criteria on which we can assess the available MP network techniques, we first define the specifics of the NoC. The first specific criterion that distinguishes a NoC from MP networks is the implementation technology. While MP networks are used for inter-chip or inter-board communications, the NoC is entirely built on the chip. Inter-chip communication requires signals to go off chip on pins. Since the number of pins available on the chip is limited to less than 1000, the number of inter-chip signals to be used for communication is also limited. In contrast, on-chip networks do not have this limitation because they are built entirely on the chip and use only on-chip wiring resources. The number of the on-chip wires available for communication signals can go far beyond the pin limitation of the inter-chip networks. For example, in 130 nm technology [92], launched in 2002, the minimum global wiring pitch is 565 nm, so there can be up to 1770 wires crossing an edge of length 1 mm on each metal layer. In 70 nm technology [93], projected in 2006, the minimum global wiring pitch is 250 nm, hence there can be up to 4000 wires crossing an edge of length 1 mm on each metal layer. Hence, on-chip networks have extensive wiring resources at their disposal compared to the traditional MP networks.

The main limitation to which the on-chip network has to conform is the chip area. While in the MP networks each router (the building block of a network) is placed on a separate chip [26, 74] and utilizes the entire chip area, all routers of an on-chip network are placed on a single chip. The NoC is just part of the implemented SoC and utilizes only part of the available chip area. The area utilized by the NoC routers should be reasonably small compared to the area used by the computational resources. The computational resources in our SoC are the processing tiles. Each tile is accompanied by a network router. As an estimate, the area of the processing tile proposed by Heysters [39] is 2 mm² in 130 nm technology. If for a maximal acceptable size for a router we assume 1/10 of the tile area, then the router area should be less than 0.2 mm².

Another NoC specific is the requirement for a simple and regular layout. The wires used for network signalling form a large part of the global on-chip wiring. To cope with the signal integrity problem, described in the introduction chapter, the global wires must be short and structured. By employing a network topology that results in a simple and regular layout, a NoC has the potential to provide wiring with well controlled parameters, predictable at an early design stage and easy to optimize. Thus, the regular layout helps in coping with the signal integrity problem.

Since the integration level provided by new semiconductor technologies increases exponentially following Moore's law, more and more tiles will fit on a single chip. Thus, the network size is also expected to grow. To provide for an easy transition between technology generations, the network must be scalable, such that it can be extended with a minimal cost and redesign efforts.

At a functional level the major difference between MP networks and the NoC is the demand for quality-of-service (QoS). In traditional multiprocessor systems, like supercomputers, the focus has been mostly on high performance, while QoS has not been an active research topic. For that reason there is a lack of MP network techniques for providing QoS. However, recently multiprocessor systems have appeared in

consumer products, such as mobile phones, TV/video sets, etc. [94]. Many program applications in these devices require QoS, and that raises the demand for QoS support.

In summary, the characteristics that distinguish the on-chip networks from the traditional MP networks are:

- large amount of available wiring resources

- area limitation for the router size

- need for regularity of the network layout

- need for scalability

- demand for QoS

# 2.3. Interconnection networks

In this section we give an overview of general techniques for the design of interconnection networks where we focus mainly on MP network techniques. The techniques are discussed within the perspective of the NoC context, in order to assess how appropriate they are for a NoC implementation.

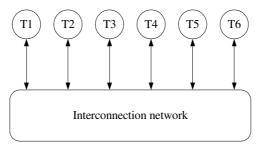

According to the definition given Dally and Towles [27], an interconnection network is a programmable system that transports data between terminals. Here terminal refers to a general source/sink of data that requires communication services. Such a system is shown in Figure 2.1. The figure shows six terminals, T1 through T6, connected to the network. When a terminal wishes to communicate data to another terminal, it sends a message containing the data over the network. The network delivers the message to the destination terminal. The network is programmable in the sense that it can make different connections at different points in time. The network in the figure may deliver a message from T3 to T5 in one cycle and use the same resources to deliver a message from T3 to T1 in the next cycle. The network is a system because it is composed of many components: buffers, channels, switches and control that work together to deliver data.

Figure 2.1: Functional view of an interconnection network

Networks meeting this broad definition may occur on many scales. However, here we restrict our attention only to small scale networks and MP networks, relevant to our SoC architecture. These networks have tens to hundreds of terminals positioned close to each other (on a board or on a chip). The terminals are processors, memories or other system modules.

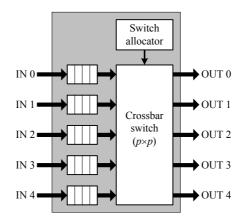

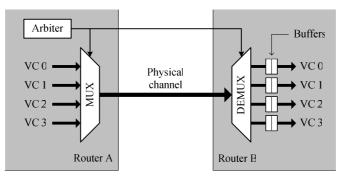

A network is built out of *switching elements* interconnected by *physical channels*, also called *links*. A switching element has a number of input and output ports. Its main function is to forward data by establishing non-conflicting connections between input and output ports. Depending on the type of network the switching elements are referred to either as *switches* or *routers*.

The physical channels are sets of wires interconnecting the ports of neighbouring routers and transporting signals between them. The physical channels form the medium that transports information in the network. The switching elements allow physical channels to be time-shared between data from different source and destination pairs. In some networks sharing may cause data blocking. To prevent loss of blocked data, the switching elements may provide storage space for temporal data buffering. The buffers may also be shared, since at different times they may store data from different sources. Besides the physical channels, buffers are the other important network resource.

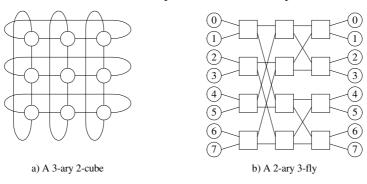

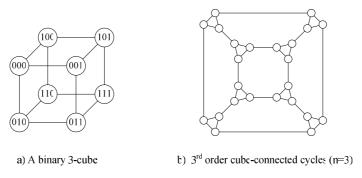

#### 2.3.1. Direct and indirect networks

A network where every switching element is directly connected to a terminal is called a *direct network*. An example of a direct network is given in Figure 2.2.a. The circles there represent pairs of terminals and switching elements, often called *nodes*. In contrast, a network where not every switching element is connected to a terminal is called an *indirect network*. An example of an indirect network is given in Figure 2.2.b. The circles represent terminal nodes and the squares represent switching elements. In indirect networks there is a natural separation between the terminals and the switching elements, while in direct networks the separation is a matter of preference.

Figure 2.2: An 8-node mesh network and an 8-node butterfly network as example of direct and indirect networks

In the topology of the tiled multiprocessor SoC architecture considered in this thesis (see Chapter 1), the tiles that construct the system are arranged into a two-dimensional array on the plane of the chip. Each tile has to be connected to the on-chip network and will play the role of a terminal. Furthermore, the network should provide simple and regular global on-chip wiring. The simplest and most natural way to satisfy these requirements is to add a switching element to each tile and to interconnect the neighbouring switching elements in a grid. This will result in a direct network topology. Therefore, we focus only on direct network topologies.

#### 2.3.2. Performance of interconnection networks

The basic metrics of the network performance are *throughput* and *latency*. Throughput is the rate at which data is delivered by the network, in [bit/s]. Throughput, also referred to as *accepted traffic*, should be clearly distinguished from the *offered traffic*. The network cannot always accept all the traffic generated by the data sources.

The *ideal throughput*,  $\theta_{ideal}$ , is the theoretical bound on the network throughput assuming that the traffic is perfectly balanced over the physical channels. However, this bound is rarely, if ever achieved because the network techniques used in practice cannot provide full network utilization, e.g. the routing cannot perfectly balance the traffic over the channels, the flow control results in idle channels because of resource dependencies, etc. Hence, the network saturates at throughput  $\theta_s$ ,  $\theta_s < \theta_{ideal}$ , referred to as *saturation throughput*.

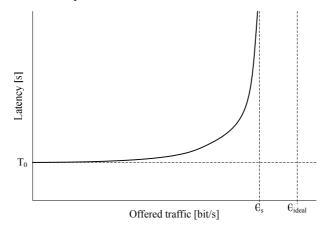

Latency is the time required for a data item to traverse the network, from the time the first bit of data arrives at the input port of the network to the time the last bit is received at the output port of the network. Often latency is estimated under a zero-load assumption; that is, data never contends for network resources. Thus zero-load latency,  $T_0$ , gives a lower bound on the data latency in the network. Figure 2.3 shows an example graph depicting a typical dependency between the traffic load offered to the network and the data latency.

Figure 2.3: Typical dependency between offered traffic and data latency in a network

## 2.3.3. Network topologies

The physical structure of a network can be represented as a graph, called a *network graph*. The vertices in the network graph represent switching elements and the edges represent physical channels. The arrangement of the switching elements and channels is represented by the topology of the network graph, called the *network topology*.

## **Definitions**

Since a network topology is represented through graphs, graph terminology is adopted when reasoning about networks. An interconnection network is formally defined as a directed graph I=(N,C), where N and C are the set of nodes and the set of channels in the graph. The *degree* of a network node is the number of channels connected to the node. When all the nodes in the network have the same degree, the network is called *degree regular*.

A *path* in the network is a sequence of nodes and channels. More formally, a path is a sequence  $\langle n_0, n_1, ... n_l \rangle$  of nodes, such that  $n_i \in N$  for  $i \in [0..l]$ , and edges  $(n_i, n_{i+1}) \in C$  for  $i \in [0..l-1]$ . Sometimes it is more convenient to express the path in terms of channels.

The path is then a sequence  $\langle c_0, c_1, ... c_{l-l} \rangle$  of channels, such that  $c_i \in C$  for  $i \in [0..l-1]$  and  $destination(c_{i-l}) = source(c_i)$  for  $i \in [1..l-1]$ . The functions  $source(c_i)$  and  $destination(c_i)$  give the source node and the destination node of the channel  $c_i$ .

The *length* of a path equals the number of channels  $(n_i, n_{i+1})$  traversed by the path. The number of traversed channels is also referred to as the *hop count*; a hop is the unit in which the network distances are usually given. Paths are also referred to as *routes*. A path between two nodes s and d is a network path  $\langle n_0, n_1, ... n_l \rangle$  such that  $n_0 = s$  and  $n_i = d$ . The *distance* between two nodes s and d is the length of the shortest path between s and d. The maximal distance D over all pairs of nodes in the network is called the *diameter* of the network – a characteristic often used for assessment and comparison of network topologies.

A *cut* of a network,  $C(N_1, N_2)$ , is a set of channels that partitions the set of all nodes N into two disjoint sets,  $N_1$  and  $N_2$ . Each element of  $C(N_1, N_2)$  is a channel with a source in  $N_1$  and destination in  $N_2$  or vice versa. The number of the channels in the cut is  $|C(N_1, N_2)|$  and the total bandwidth of the cut is:

(2.1)

$$B(N_1, N_2) = \sum_{c \in C(N_1, N_2)} b_c,$$

where  $b_c$  is the bandwidth of channel c.

A *bisection* of a network is a cut that partitions the network nearly in half, such that  $|N_2| \le |N_I| \le |N_2| + 1$ . The *channel bisection*,  $B_C$ , of a network is the minimum channel count over all bisections of the network:

$$(2.2) B_C = \min_{\text{historians}} |C(N_1, N_2)|.$$

The bisection bandwidth,  $B_B$ , of a network is the minimum bandwidth over all bisections of the network:

$$(2.3) B_B = \min_{bisections} B(N_1, N_2).$$

For networks with uniform channel bandwidth  $b_c=b$  for every  $c \in C$ , the bisection bandwidth is  $B_B=bB_C$ . For simplicity, in the following sections we refer to the channel bisection only as bisection unless explicitly stated otherwise.

A topology characteristic related to the bisection is the network *connectivity*. A network is called k-connected when between any pair of nodes there exist at least k paths that do not share other nodes than the source and the destination (internally vertex disjoint paths). The maximal k for the network is called the connectivity of the network. Since the connectivity corresponds to the path diversity between the nodes, it is used as a measure of the fault-tolerance of the network. On the other hand, it can also be used as a network performance measure related to the bisection.

#### Requirements

The selection of the network topology will be driven by the following criteria:

Small and fixed degree. The degree of a node determines the number of ports

of the corresponding switching element. Hence, node degree influences the

switching element complexity and area cost. A small degree reduces the cost.

Degree regularity allows for uniform design of the switching elements.

- Simple and uniform layout. Whatever the topology, the network is embedded in the plane of the chip. The layout of the embedded network defines the global on-chip wiring, which has to be as simple and uniform as possible in order to lessen the signal integrity problem.

- Small diameter. Networks with a smaller diameter have shorter distances and therefore lower communication latency.

- Simple routing. The network topology influences the algorithm used for searching routes in the network. Regularity and simplicity of the network topology can simplify the routing algorithm

- Scalability. Following Moore's law, the number of system components onchip is expected to increase exponentially with the technology generations in the next 10 years [93]. Thus, the number of nodes in the on-chip network will increase. To provide easy transition between technology generations, the topology should support extension (an increase in the number of nodes) at minimal cost and redesign efforts.

- Fault tolerance. Defects in the manufacturing process may cause malfunctioning or failure of network components (channels or routers) in newly produced chips. To reduce the impact of such defects on the production yield, it is desirable that in the presence of a reasonably small number of faulty components, the network is still operable. During its operation, the network should be able to avoid the faulty components by using alternative paths. The presence of alternative paths is indicated by the connectivity of the network; hence, topologies with higher connectivity are preferable.

Having motivated our requirements for a topology, we continue by giving an overview of direct network topologies most commonly used in MP networks.

#### Tree topologies

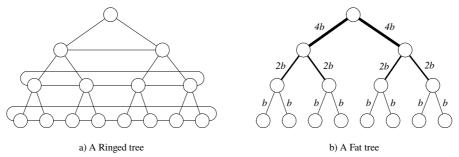

As the name suggests, the tree topology interconnects the network nodes in the form of a tree. Each node (except the root) has one ancestor and k descendants. A tree in which every node, except the leaves, has exactly k descendants is a k-ary tree. Tree networks have a small diameter,  $O(\log_k N)$ , N being the number of nodes in the network, but their bisection and connectivity are small, only 1; there is only one path available between any pair of nodes. Therefore, the network is not fault-tolerant. To improve the fault tolerance, *ringed trees* have been proposed [29]. As shown in Figure 2.4.a, a ringed tree connects the nodes of each stage of the tree in a ring.

Figure 2.4: Tree topologies

The small bisection of the trees also causes performance problems. The nearer to the root a channel is, the more paths use it. Therefore, the channels nearer to the root have a higher load and become a bottleneck. To overcome this problem, fat-trees have been proposed [51]. In fat-trees, channels that are nearer to the root have higher bandwidth. For example, in the fat-tree shown in Figure 2.4.b, the channels connecting the leaves of the tree have bandwidth b, the channels connecting the next stage have bandwidth 2b, and so on. While fat-trees overcome the tree performance problem, they introduce irregularity in the physical design of the switching elements and do not improve the fault-tolerance.

#### Star topologies

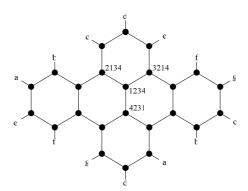

A star graph [11] has n! nodes labelled by permutations of n different symbols. Each node in the graph is connected to n-1 other nodes, with labels that are obtained from the current node label by interchanging the first symbol and one of the other symbols. An example of a four-star graph (n=4) is given in Figure 2.5. The nodes are labelled by permutations of the symbols  $\{1, 2, 3, 4\}$ . Labels are shown only for one node and its three neighbours. The border edges labelled by the same letter are connected, but for clarity of representation the connecting edges are not shown.

The degree of an n-star graph is n-1 and the diameter is  $\lfloor 3(n-1)/2 \rfloor$ . Although, the degree and the diameter of star graph are lower than the degree and the diameter of mesh and torus network (discussed below) of similar sizes, the routing is more complicated and the node degree depends on the network size.

Figure 2.5: An example of star graph

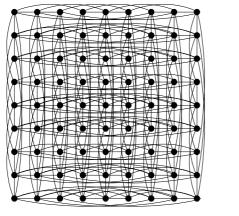

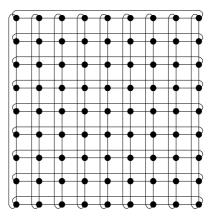

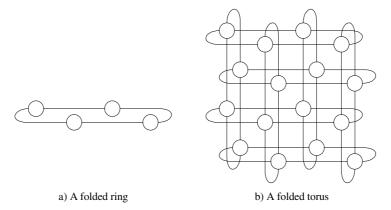

## Torus and mesh topologies

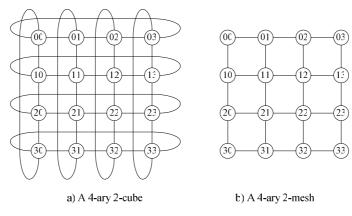

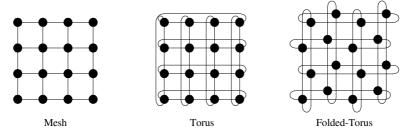

Among the direct network topologies, torus and mesh networks are the most popular, well studied and often used for practical implementations. Torus networks are characterised by their radix k and the number of dimensions n. An n-dimensional radix-k torus, also referred to as a k-ary n-cube, arranges  $N=k^n$  nodes in a n-dimensional cube with k nodes in each dimension. Each node is assigned an n-digit radix-k address  $\{a_{n-1}, \ldots, a_0\}$ . The ith digit in the address,  $a_i$ , represents the node position in the ith dimension. A node is connected by a pair of channels (one in each direction) to all nodes with

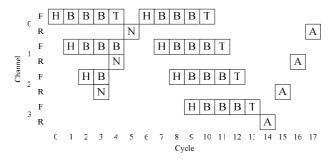

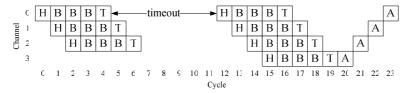

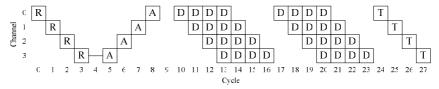

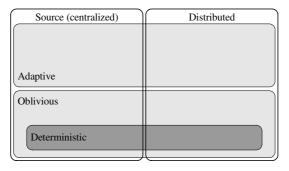

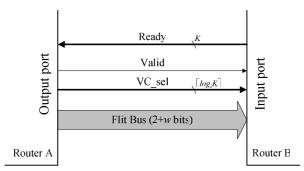

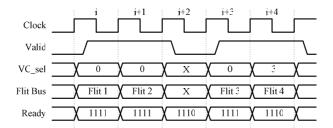

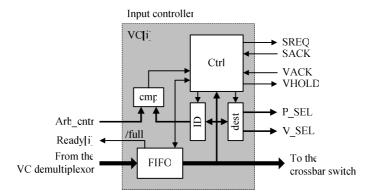

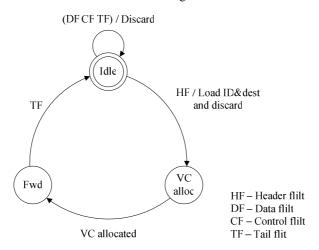

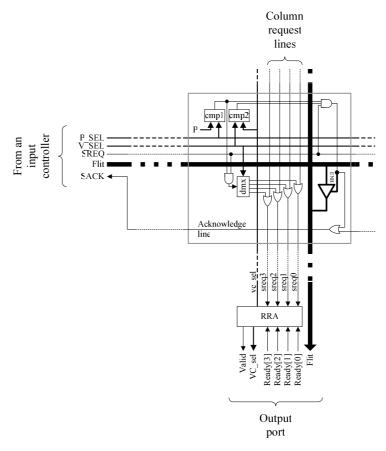

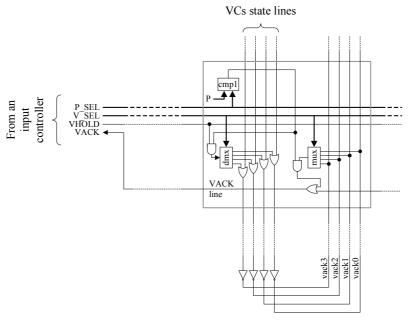

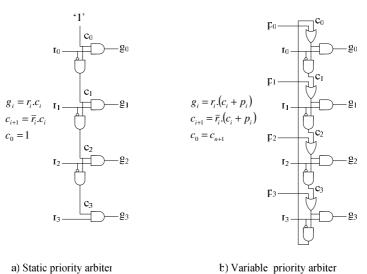

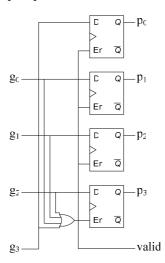

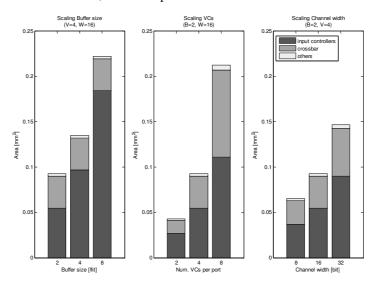

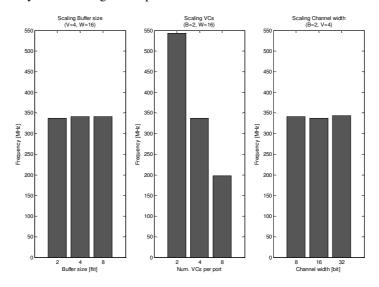

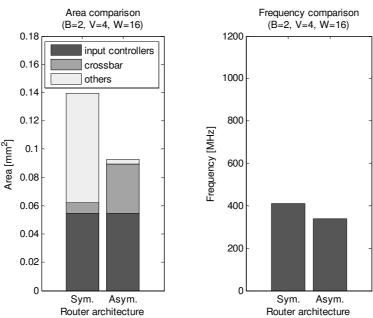

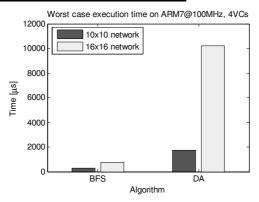

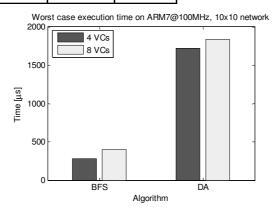

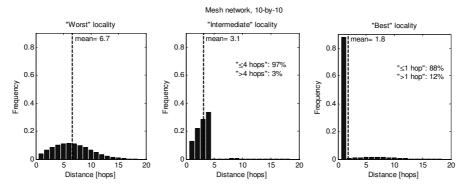

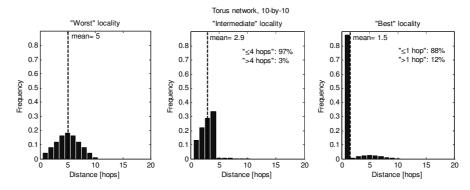

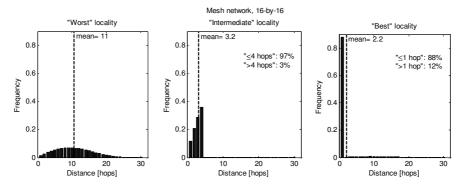

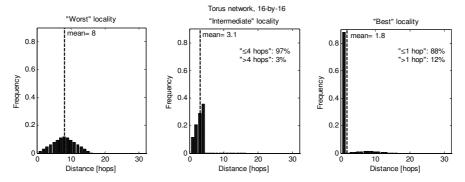

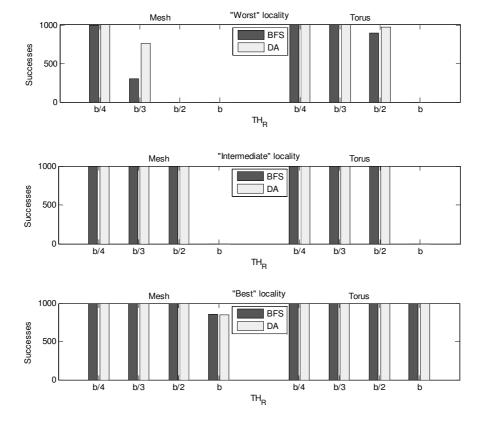

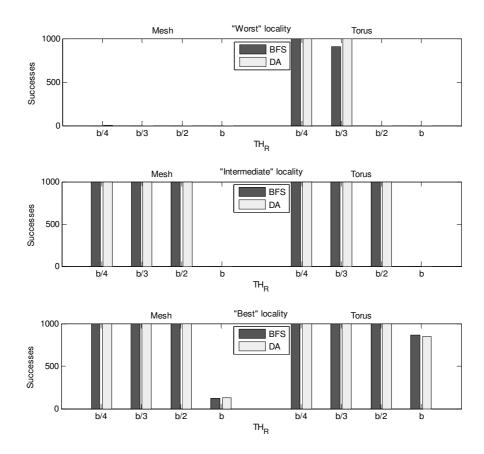

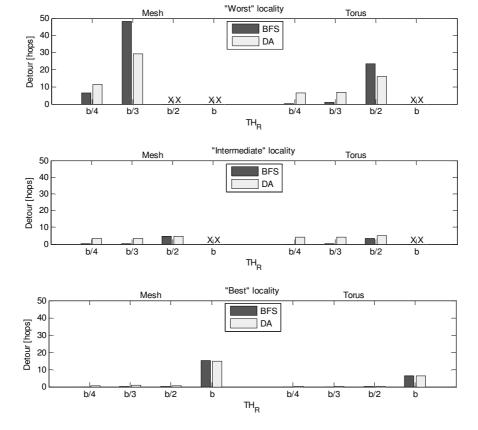

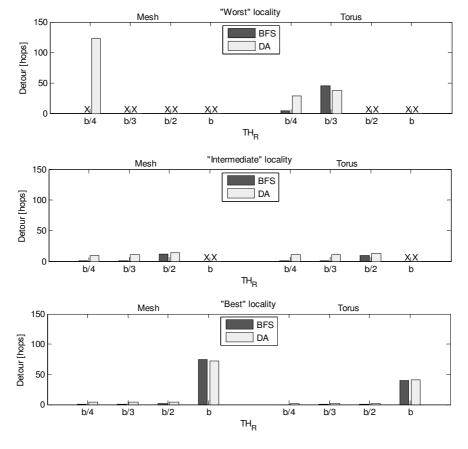

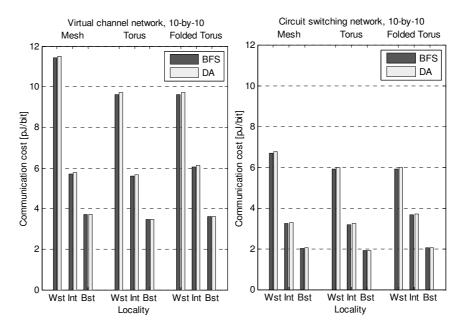

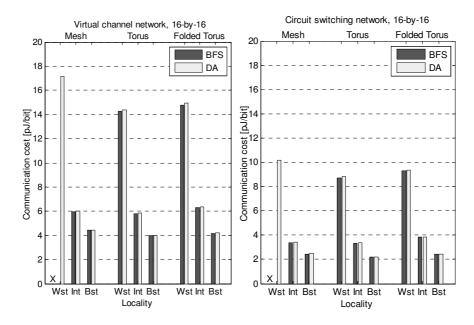

addresses that differ by  $\pm 1 \pmod{k}$  in exactly one address digit. This requires 2 channels in each dimension per node or 2n channels. Tori are degree regular, their diameter is  $n \lfloor k/2 \rfloor$  hops and the bisection is  $4N/k = 4k^{n-1}$ . An example of a 4-ary 2-cube is given in Figure 2.6.a. The long channels connecting the nodes on the opposite edges of the node array are usually referred to as wraparound channels.